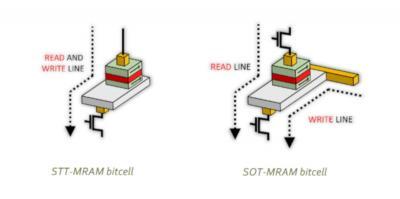

Researchers exploit the Orbital Hall Effect to increase the performance of SOT-MRAM devices

Researchers from the Johannes Gutenberg University Mainz (JGU) in Germany, in collaboration with Antaios, have developed a new SOT-MRAM based platform that enables highly efficient and powerful data processing and storage.

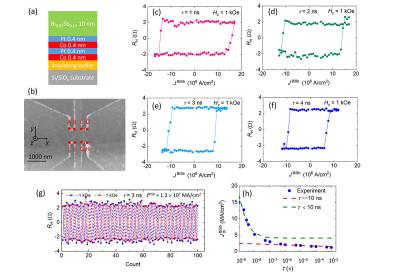

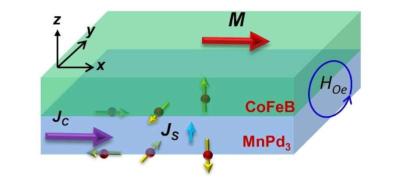

By exploiting previously neglected orbital currents, the researchers have developed a unique magnetic material incorporating elements such as Ruthenium as a SOT channel—a fundamental building block of SOT MRAM—to significantly enhance performance.