NTU and TSMC researchers develop a new SOT-MRAM structure with high spin-orbital Hall conductivity

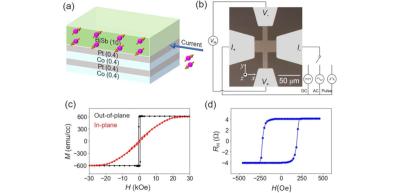

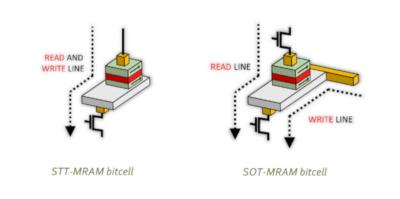

Researchers from National Taiwan University in collaboration with TSMC developed a new SOT-MRAM device structure, that features sizable orbital currents. This research promises a pathway for enhancing SOT-MRAM performance by harnessing both the conventional spin currents and the emergent orbital currents.

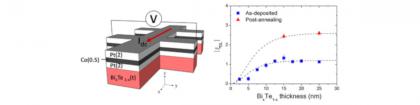

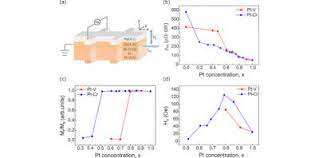

The new device is based on 3d light transition metals (such as V and Cr) that are incorporated into the classical spin Hall metal Pt. The Pt-Cr alloy enhances the charge-to-spin conversion efficiency which can realize high spin-orbital Hall conductivity, beyond the conventional spin Hall limit.

The new device is based on 3d light transition metals (such as V and Cr) that are incorporated into the classical spin Hall metal Pt. The Pt-Cr alloy enhances the charge-to-spin conversion efficiency which can realize high spin-orbital Hall conductivity, beyond the conventional spin Hall limit.