Renesas Electronics announced that it has developed two new technologies that reduce the energy and voltage application time for the write operation of STT-MRAM chips.

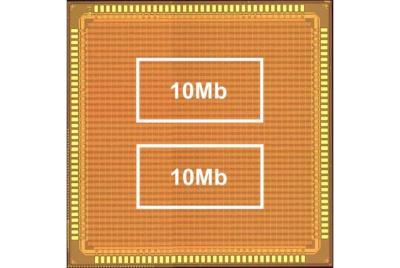

On a 20-Mbit test chip with embedded MRAM memory cell array in a 16 nm FinFET logic process, a 72% reduction in write energy and a 50% reduction in the voltage application time were confirmed.

The new technologies are:

- A self-termination write scheme with slope pulse application, in which the write pulse is automatically and adaptively terminated due to write characteristics of each memory cell;

- A write sequence to optimize the number of bits, to which write voltage is applied simultaneously. Combined, these technologies make it possible to reduce the power consumption and increase the speed of write operations.

Renesas says it will continue to develop incremental embedded MRAM technologies, and will endeavor to further increase capacity, speed, and power efficiency to accommodate a range of new applications.

Posted: Dec 16,2021 by Ron Mertens