Intel researchers have demonstrated 2MB STT-MRAM devices that are suitable for on-chip L4 cache applications. Intel says these devices feature data retention, endurance and bit error rates good enough for L4 cache.

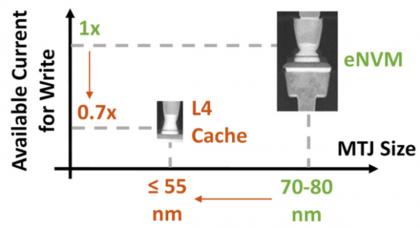

Intel's new STT-MRAM features 20 nm write times, 4 ns read times, an endurance of 1012 cycles and memory retention of one second at 110 degrees. The bit rates are good enough to be handled with error-correcting code (ECC) techniques. To achieve these features, Intel reduced the magnetic junction size to 55 nm (from 70-80 nm it had achieved before).

Source:

Posted: Dec 11,2019 by Ron Mertens