New research may hold the key towards antiferromagnetic MRAM

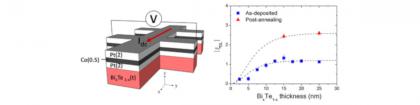

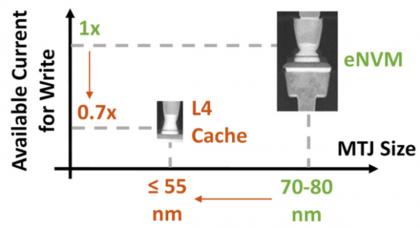

Researchers from the University of Arizona discovered that in common Magnetic Tunnel Junctions (MTJ), there's a thin (2D) layer of Iron Oxide. This layer was found to act as a contaminant which lowers the performance achieved by MTJs, but it may also hold the key to use antiferromagnetism in MRAM devices.

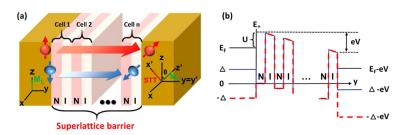

The researchers discovered that the layer behaves as a so-called antiferromagnet at extremely cold temperatures (below -245 degrees Celsius). Antiferromagnets are promising as these can be manipulated at Terahertz frequencies, about 1,000 times faster than existing, silicon-based technology. This is the first research that shows how Antiferromagnets can be controlled as part of MTJs and in the future may pave the way for its adoption in MRAM devices.