Researchers from Samsung will soon present at IEDM 2022 a new research paper that will discuss the company's latest achievements in scaling down its MRAM technology to the company's 14nm FinFET logic process.

The Samsung researchers produced a stand-alone memory with a write energy requirement of 25 pJ per bit and active power requirements of 14 mW for reading and 27 mW for writing at a 54Mbyte per second data rate. The cycling is 10^14 cycles and when scaled to a 16Mbit device, a chip would occupy 30 square millimeters.

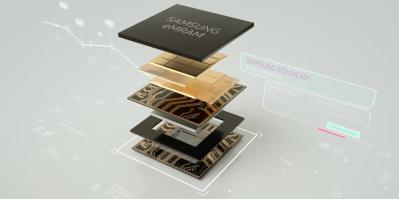

To achieve this performance the research team scaled the magnetic tunnel junction down to Samsung’s 14nm FinFET logic platform resulting in a 33 percent improvement in area and 2.6x faster read times compared to the 28nm predecessor.

In March 2019 Samsung Electronics announced that it has started to mass produce its first embedded MRAM devices, made using the company's 28nm FD-SOI process. In early 2021 Samsung announced that it managed to improve the MTJ function of its MRAM, which makes it suitable for more applications. Later in 2021, Samsung provides more details on its MRAM roadmap and announced it is working to scale down to 14nm processes.