Successful MRAM Production Requires Good Magnetic Test Equipment

This is a sponsored post by Integral Solutions Int'l

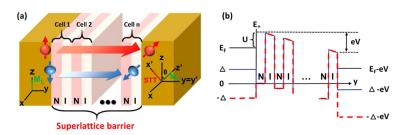

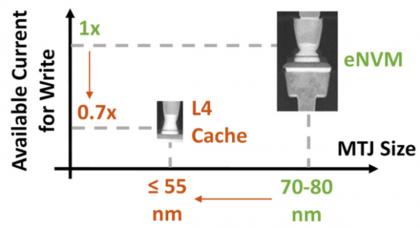

MRAM is likely to be the most promising next-generation non-volatile memory technology today. Toggle MRAM and STT-MRAM are already entering the market, gaining market share in many applications. Next-generation MRAM technologies, such as SOT-MRAM could enable the replacement of even the fastest SRAM applications, with higher densities.

Source: Coughlin Associates, 2019

Source: Coughlin Associates, 2019

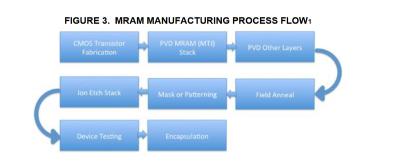

The MRAM production process has many stages, as device architecture is relatively complex, with a magnetic cell (frontplane) fabricated on top of a CMOS backplane. (use Figure 2 or Figure 3 from Coughlin). Measurement and characterization of devices are highly important, and the production of MRAM memories depend on measurement tools are are specialized for MRAM and STT-MRAM measurements.