A*STAR patents low-density parity-check (LDPC) coding with soft decision decoding for STT-MRAM devices

A*STAR scientists have filed a patent on low-density parity-check (LDPC) coding with soft decision decoding. This is an advanced error correction coding scheme STT-MRAM devices. Hopefully this new scheme will enable more relaxed smaler STT-MRAM designs that can rely on the error-correction.

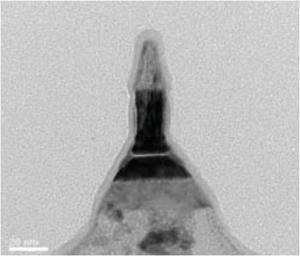

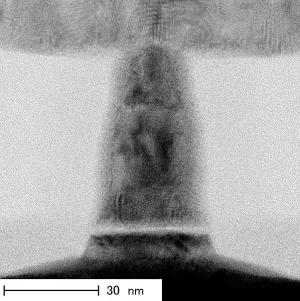

STT-MRAM devices suffer from cell errors due to imperfections in the fabrication process (variation in the tunneling oxide thickness and cross-section area). The researchers explain that conventional (hard decision) error correction codes do not work very well on STT-MRAM cells. The new soft decision decoding works on the probability of each detected bit as being a 0 or 1 (i.e. soft reliability), and hence has less decoding errors than the conventional hard decision decoding.