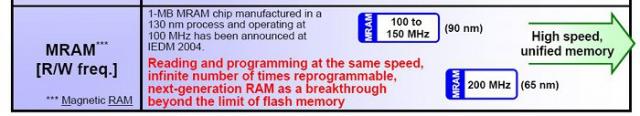

In addressing the need for next-generation high-density on-chip non-volatile memory Technology, Hitachi, Ltd. and Renesas today announced the development of a 512-kbyte (4-Mbit equivalent) phase change memory module operating at a 1.5-V power supply voltage, which achieves 416-kbyte/sec high-speed write and read speeds with a 20-nanosecond access time. Using the previously developed "low-power phase change memory cells" with a 100-uA (micro(2)-ampere) write current, the two companies developed a peripheral circuit Technology to enable the high-speed write and read operations.

In addressing the need for next-generation high-density on-chip non-volatile memory Technology, Hitachi, Ltd. and Renesas today announced the development of a 512-kbyte (4-Mbit equivalent) phase change memory module operating at a 1.5-V power supply voltage, which achieves 416-kbyte/sec high-speed write and read speeds with a 20-nanosecond access time. Using the previously developed "low-power phase change memory cells" with a 100-uA (micro(2)-ampere) write current, the two companies developed a peripheral circuit Technology to enable the high-speed write and read operations.

An experimental 512-kbyte memory module was fabricated using a 130-nm CMOS process, employing the newly developed circuit Technology for cells writable at 100 uA. Test results confirmed the possibility of 416-kbyte/sec write operations and 20-nanosecond read operations, and high-speed operation was achieved while maintaining the Performance of low-power-operation phase change memory cells.