Taiwan's Semiconductor Research Institute developed an SOT-MRAM device based on a PMA technique

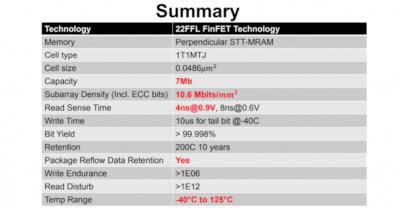

Researchers at Taiwan's Semiconductor Research Institute (TSRI) unveiled a new SOT-MRAM memory device that they developed in collaboration with University scientists.

The new device uses a perpendicular magnetic anisotropy (PMA) technique. According to the TSRI researchers, they are the second team to successfully produce MRAM chips based on PMA (Intel is the first team to have achieved this).